---

# СИСТЕМНЫЙ АНАЛИЗ, УПРАВЛЕНИЕ И ОБРАБОТКА ИНФОРМАЦИИ

## SYSTEM ANALYSIS, CONTROL, AND INFORMATION PROCESSING

---

УДК 004.052.32+681.518.5

DOI: 10.17586/0021-3454-2025-68-4-279-295

### ИССЛЕДОВАНИЕ СВОЙСТВ ДВУХМОДУЛЬНЫХ ВЗВЕШЕННЫХ КОДОВ С СУММИРОВАНИЕМ В СХЕМАХ ВСТРОЕННОГО КОНТРОЛЯ НА ОСНОВЕ ЛОГИЧЕСКОЙ КОРРЕКЦИИ СИГНАЛОВ

Д. В. Ефанов<sup>1,2\*</sup>, М. В. Зуева<sup>3</sup>, Е. И. Елина<sup>2</sup>, М. В. Тимошенков<sup>2</sup>

<sup>1</sup> Российский университет транспорта, Москва, Россия

<sup>2</sup> Санкт-Петербургский политехнический университет Петра Великого, Санкт-Петербург, Россия

<sup>3</sup> Банк „Санкт-Петербург“, Санкт-Петербург, Россия

\* TrES-4b@yandex.ru

**Аннотация.** Рассматриваются особенности применения двухмодульных кодов с суммированием при синтезе самопроверяемых цифровых устройств. Показано, что применение двухмодульных кодов с суммированием существенно расширяет число способов синтеза схем встроенного контроля как по традиционному варианту построения с дополнением информационных векторов контрольными, так и по альтернативному, основанному на принципе логической коррекции сигналов. Установлены ранее неизвестные характеристики обнаружения ошибок двухмодульными кодами с суммированием в кольце вычетов по модулю  $M = 4$  при „половинном разбиении“ информационных символов на два подмножества. Показано, что число потенциальных необнаруживаемых ошибок в кодовых словах двухмодульных кодов с суммированием в десятки раз больше числа необнаруживаемых ошибок, возникающих исключительно в информационных символах кодовых слов. Эту особенность целесообразно использовать при синтезе схем встроенного контроля на основе логической коррекции сигналов путем выделения группы выходов, сигналы с которых корректируются в схеме встроенного контроля. Приводится правило выделения функционально независимых групп выходов объекта диагностирования. Сформирован обобщенный алгоритм синтеза схем встроенного контроля на основе логической коррекции сигналов с применением двухмодульных взвешенных кодов с суммированием. В эксперименте показано, что с помощью двухмодульных взвешенных кодов с суммированием можно получать более простые самопроверяемые устройства, чем при использовании классических подходов. Полученные в ходе исследования результаты могут эффективно использоваться при разработке самопроверяемых цифровых устройств и вычислительных систем.

**Ключевые слова:** самопроверяемые устройства, схема встроенного контроля, контроль вычислений, обнаружение ошибок на выходах устройств, необнаруживаемая ошибка, двухмодульный взвешенный код с суммированием, характеристики обнаружения ошибок

**Ссылка для цитирования:** Ефанов Д. В., Зуева М. В., Елина Е. И., Тимошенков М. В. Исследование свойств двухмодульных взвешенных кодов с суммированием в схемах встроенного контроля на основе логической коррекции сигналов // Изв. вузов. Приборостроение. 2025. Т. 68, № 4. С. 279–295. DOI: 10.17586/0021-3454-2025-68-4-279-295.

### STUDY OF PROPERTIES OF WEIGHT-BASED TWO-MODULE SUM CODES IN CONCURRENT ERROR-DETECTION CIRCUITS BASED ON BOOLEAN SIGNAL CORRECTION

D. V. Efano<sup>1,2\*</sup>, M. V. Zueva<sup>3</sup>, Y. I. Yelina<sup>2</sup>, M. V. Timoshenkov<sup>2</sup>

<sup>1</sup> Russian University of Transport, Moscow, Russia

<sup>2</sup> Peter the Great St. Petersburg Polytechnic University, St. Petersburg, Russia

<sup>3</sup> Bank Saint Petersburg, St. Petersburg, Russia

\* TrES-4b@yandex.ru

**Abstracts.** The features of the application of two-module sum codes in the synthesis of self-checking digital devices are considered. It is shown that the use of two-module sum codes significantly expands the number of ways to synthesize concurrent error-detection circuit both according to the traditional structure with the addition of data vectors with test ones, and according to an alternative one based on the principle of Boolean signals correction. Previously unknown characteristics of error detection by two-module sum codes in the residue ring modulo  $M = 4$  with a “half division” of data symbols into two subsets have been established. It is shown that the number of potential undetectable errors in the codewords of two-module sum codes is ten times greater than the number of undetectable errors that occur exclusively in the data symbols of codewords. It is advisable to use this feature in the synthesis of concurrent error-detection circuit based on the Boolean signals correction by selecting a group of outputs, the signals from which are corrected in the concurrent error-detection circuit. The rule of allocation of functionally independent groups of outputs of the diagnostic object is applied. A generalized algorithm for the synthesis of concurrent error-detection circuit based on the Boolean signal's correction using two-module weight-based sum codes has been formed. The experiment shows that using two-module weight-based sum codes, it is possible to obtain less redundant self-checking devices than using classical approaches. The results obtained in the course of the study can be effectively used in the development of self-checking digital devices and computing systems.

**Keywords:** self-checking devices, concurrent error-detection circuit, calculation control, error detection at device outputs, undetectable error, two-module weight-based sum code, error detection characteristics

**For citation:** Efanova D. V., Zueva M. V., Yelina Y. I., Timoshenkov M. V. Study of Properties of Weight-based Two-module Sum Codes in Concurrent Error-Detection Circuits Based on Boolean Signal Correction. *Journal of Instrument Engineering*. 2025. Vol. 68, N 4. P. 279–295 (in Russian). DOI: 10.17586/0021-3454-2025-68-4-279-295.

**Введение.** Самопроверяемые устройства и системы строятся с применением методов резервирования (структурного, информационного, временного), в том числе широко используются методы помехозащищенного и помехоустойчивого кодирования [1–3].

Для контроля вычислений самопроверяемыми устройствами избыточность либо вносится в сам исходный объект (объект диагностирования), либо добавляется в виде внешних устройств контроля — отдельных тестеров или целых схем встроенного контроля (СВК), которые также содержат тестеры. Одним из направлений практического применения теории синтеза самопроверяемых устройств и систем является использование двоичных равномерных кодов при синтезе СВК [4]. Разнообразие таких кодов с малой избыточностью позволяет синтезировать различные по характеристикам СВК и, как следствие, высоконадежные устройства и системы [5, 6]. В настоящей статье рассматриваются только так называемые *двуходульные коды с суммированием*<sup>1</sup>.

Двуходульные коды с суммированием разрабатывались для применения именно при синтезе контролепригодных и самопроверяемых устройств, поскольку они ориентированы исключительно на обнаружение ошибок в кодовых словах при малой избыточности [7, 8]. Построение двухмодульного кода с суммированием позволяет для отдельных двух групп информационных символов сформировать отдельные группы проверочных символов, обеспечивая тем самым покрытие ошибок в них „по отдельности“. Фактически при применении таких кодов в процессе синтеза СВК выходы объектов диагностирования разделяются на группы внутри контрольных устройств без их непосредственного физического разделения. То, на какие подмножества окажется разбитым множество информационных символов кода, зависит от выбранного способа построения двухмодульного кода.

В [7, 8] разработаны двухмодульные коды с суммированием единичных информационных разрядов, а в [9] — двухмодульные взвешенные коды с суммированием. При их построении использовано разбиение множества разрядов  $m$ -разрядного информационного вектора на два непересекающихся подмножества, содержащих  $\left\lceil \frac{m}{2} \right\rceil$  и  $\left\lfloor \frac{m}{2} \right\rfloor$  разрядов, с последующим подсчетом для каждой группы значения веса в кольце вычетов по модулю  $M = 4$ . Такие коды при любых значениях  $m$  имеют  $k = 4$  проверочных символа, а общее число символов в кодовых словах равно  $n = m + k = m + 4$ . В [10] определены характеристики и свойства двухмодульных взвешенных

<sup>1</sup> Более точно: данные коды следует отнести к кодам с контролем отдельных (двух) групп информационных символов по заданным модулям.

кодов с суммированием в кольце вычетов по модулю  $M = 4$ , которые проявляются при изменении числа  $t$  с учетом разбиений множества информационных векторов на подмножества с различной мощностью. Двухмодульные коды более эффективны, чем классические коды с суммированием, или коды Бергера [11], и некоторые их модификации [12].

Целью настоящей статьи является исследование особенностей реализации СВК на основе логической коррекции сигналов (ЛКС) [13, 14] с использованием двухмодульных взвешенных кодов с суммированием в кольце вычетов по модулю  $M = 4$ , построенных при взвешивании только одного из символов в каждом выделяемом подмножестве информационных символов при „половинном разбиении“. Далее будет показано, что применение двухмодульных взвешенных кодов с суммированием позволяет синтезировать большое количество структур СВК на основе ЛКС, что дает возможность решать на практике наиболее сложную задачу обеспечения полной самопроверяемости реализуемого устройства.

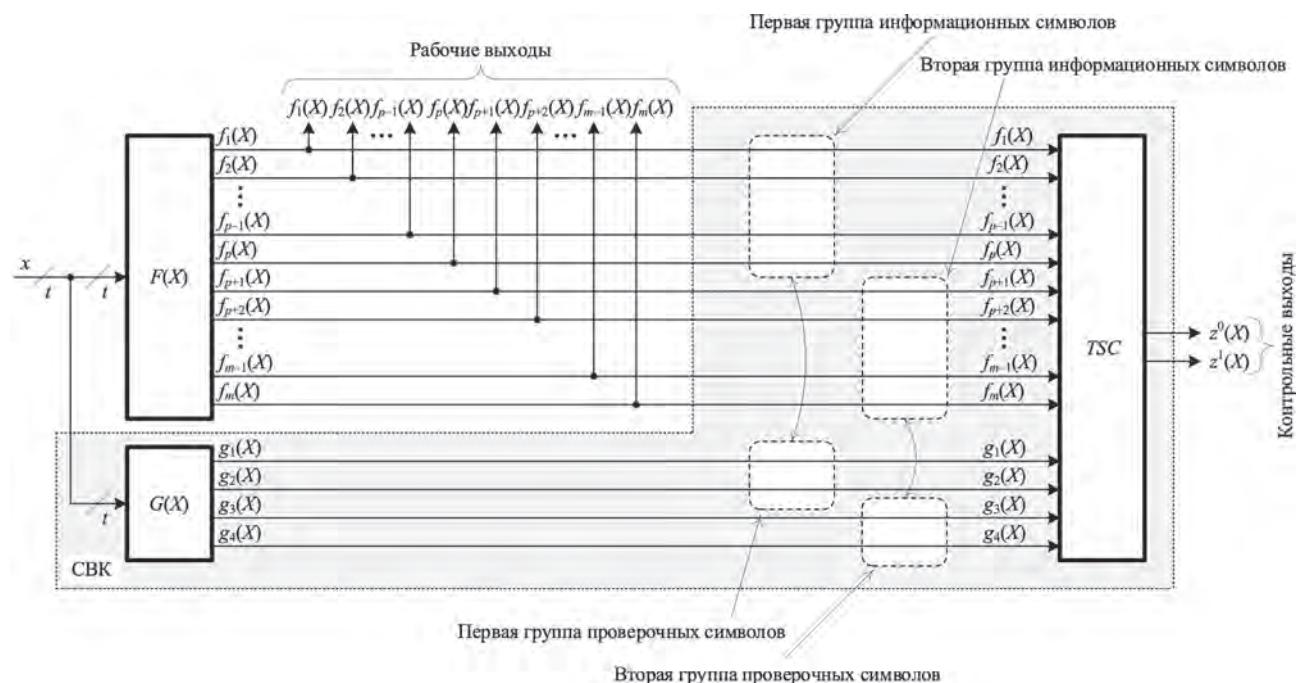

**Синтез схем встроенного контроля на основе логической коррекции сигналов и двухмодульных взвешенных кодов с суммированием.** При использовании двухмодульных кодов с суммированием для синтеза СВК в общем случае (без выделения групп выходов) могут использоваться две основные структурные схемы, приведенные на рис. 1 и 2.

Рис. 1

Первый вариант построения (рис. 1) является традиционным (классическим) [15], он основан на дополнении в СВК информационного вектора, формируемого на выходах объекта диагностирования  $F(X)$ , до кодового слова двухмодульного кода (по сути, конкатенации информационного и контрольного векторов). В этом случае проверочные символы, объединяемые в контрольный вектор, вычисляются блоком контрольной логики  $G(X)$ . Далее информационные и проверочные символы в СВК сравниваются между собой с применением схемы тестера TSC (totally self-checking checker).

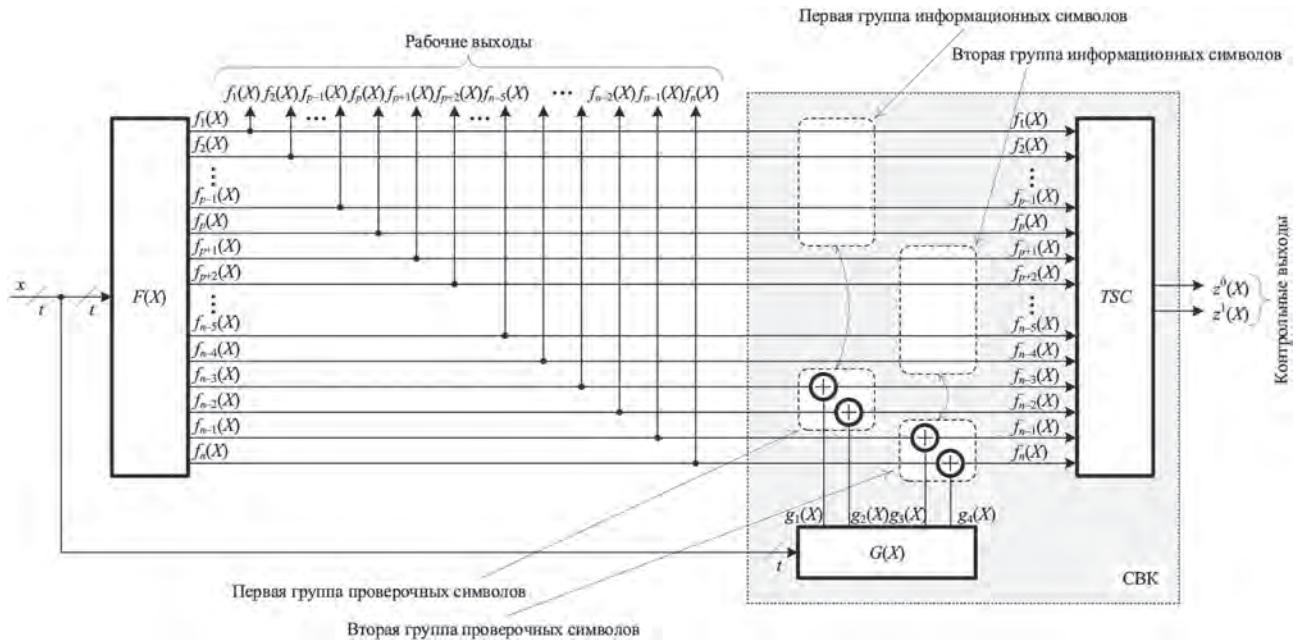

Второй вариант построения (рис. 2) является альтернативным [3, 13, 14], он основан на применении принципа ЛКС: использовании логической коррекции части или всех сигналов от объекта диагностирования в СВК в целях получения кодового слова двухмодульного кода с суммированием. Наиболее простой случай реализации данного варианта — преобразование сигналов только с тех выходов объекта диагностирования, которые отвечают за формирование проверочных символов кодовых слов. Именно такой случай приведен на рис. 2. Требуется всего

четыре элемента преобразования (*XOR*), и соответственно четыре функции логической коррекции, для получения любого кодового слова двухмодульного кода с суммированием из любого вектора, формируемого на выходах объекта диагностирования. Это, в свою очередь, упрощает процедуру обеспечения полной самопроверяемости СВК по сравнению с коррекцией большего числа сигналов, поскольку при построении СВК требуется обеспечить тестируемость элементов преобразования (подачу тестовых комбинаций из множества {00, 01, 10, 11} для элементов *XOR* при их канонической реализации [16])<sup>2</sup>.

Рис. 2

При построении СВК на основе рис. 1 и двухмодульного кода с суммированием имеется некоторая „гибкость“ в обеспечении самопроверяемости и выбора наиболее простого блока контрольной логики  $G(X)$ , в отличие от применения классического или модульного кода с суммированием [18]. Это связано с особенностями построения двухмодульного кода с суммированием.

Если рассматривается устройство с  $t$  выходами, то согласно правилам построения двухмодульного кода [9] выделяются две группы из  $\left\lfloor \frac{m}{2} \right\rfloor$  и  $\left\lceil \frac{m}{2} \right\rceil$  выходов. Среди  $t$  выходов можно выделить  $\left\lfloor \frac{m}{2} \right\rfloor$  выходов  $C_m^{\left\lfloor \frac{m}{2} \right\rfloor}$  способами. Взвешиваемый разряд в первом информационном подвекторе может быть выбран  $C_{\left\lfloor \frac{m}{2} \right\rfloor}^1 = \left\lfloor \frac{m}{2} \right\rfloor$  способами, а взвешен — тремя, поскольку  $w \in \{1, 2, 3\}$  при  $M = 4$ . Оставшиеся  $\left\lceil \frac{m}{2} \right\rceil$  выходов во втором подвекторе выбираются единственным способом:  $C_{\left\lceil \frac{m}{2} \right\rceil}^1 = 1$ . Взвешиваемый разряд выбирается  $C_{\left\lceil \frac{m}{2} \right\rceil}^1 = \left\lceil \frac{m}{2} \right\rceil$  способами, а значение весового коэффициента также тремя. Итого имеем следующее количество способов построения двухмодульного кода и, как следствие — самой СВК, согласно рис. 1:

<sup>2</sup> Если рассматривать не каноническую реализацию *XOR*, а, например, из [17], на трех транзисторах, то для его тестирования достаточно трех комбинаций: либо {00, 01, 11}, либо {00, 01, 10}, либо {00, 10, 11}, либо {01, 10, 11}.

$$\begin{aligned}

V_m &= 9C_m^{\left\lfloor \frac{m}{2} \right\rfloor} \left[ \frac{m}{2} \right] \left[ \frac{m}{2} \right] = \frac{9m!}{\left[ \frac{m}{2} \right]! \left( m - \left[ \frac{m}{2} \right] \right)!} \left[ \frac{m}{2} \right] \left[ \frac{m}{2} \right] = \\

&= \frac{9m!}{\left[ \frac{m}{2} \right]! \left[ \frac{m}{2} \right]!} \left[ \frac{m}{2} \right] \left[ \frac{m}{2} \right] = \frac{9m!}{\left( \left[ \frac{m}{2} \right] - 1 \right)! \left( \left[ \frac{m}{2} \right] - 1 \right)!}.

\end{aligned} \tag{1}$$

К примеру, для  $m = 21$  формула (1) дает следующий результат:

$$V_{21} = 9C_{21}^{\left\lfloor \frac{21}{2} \right\rfloor} \left[ \frac{21}{2} \right] \left[ \frac{21}{2} \right] = \frac{9 \cdot 21!}{\left( \left[ \frac{21}{2} \right] - 1 \right)! \left( \left[ \frac{21}{2} \right] - 1 \right)!} = \frac{9 \cdot 21!}{9!10!} = 349\,188\,840.$$

При построении варианта на основе ЛКС также имеется большая гибкость в обеспечении самопроверяемости СВК и в оптимизации показателей структурной избыточности. Если число непреобразуемых выходов равно  $m$ , то количество способов построения СВК можно подсчитать по формуле (1). Преобразуемые выходы можно выбрать  $C_{m+4}^4$  способами. Четыре выделенных преобразуемых выхода можно переставить  $P_4 = 4! = 24!$  способами. Таким образом, число способов синтеза СВК на основе рис. 2 составит:

$$R_m = \frac{9m! P_4 C_{m+4}^4}{\left( \left[ \frac{m}{2} \right] - 1 \right)! \left( \left[ \frac{m}{2} \right] - 1 \right)!} = \frac{216(m+4)!}{\left( \left[ \frac{m}{2} \right] - 1 \right)! \left( \left[ \frac{m}{2} \right] - 1 \right)!}. \tag{2}$$

Для случая  $m = 21$  по формуле (2) имеем такое число способов организации СВК согласно рис. 2:

$$R_{21} = \frac{216 \cdot 25!}{\left( \left[ \frac{21}{2} \right] - 1 \right)! \left( \left[ \frac{21}{2} \right] - 1 \right)!} = \frac{216 \cdot 25!}{9!10!} = 2\,544\,329\,563\,776\,000.$$

Если рассматривается устройство с 21 выходом, то по рис. 1 выделяется 21 выход для формирования информационных символов, а по рис. 2 — 17 выходов. Тогда для второго случая будем иметь такое число способов построения СВК:

$$R_{17} = \frac{216 \cdot 21!}{\left( \left[ \frac{17}{2} \right] - 1 \right)! \left( \left[ \frac{17}{2} \right] - 1 \right)!} = \frac{216 \cdot 21!}{7!8!} = 54\,305\,848\,396\,800.$$

Полученное число также больше числа способов организации СВК при использовании классического варианта для 21 выхода — примерно в 155 520 раз. При этом тестер в СВК будет гораздо проще тестера, используемого в классическом варианте.

Характеристики обнаружения ошибок двухмодульными взвешенными кодами с суммированием в информационных символах при условии отсутствия ошибок в проверочных символах, которые используются в классическом варианте построения СВК, рассмотрены в [9]. Обратимся к характеристикам обнаружения ошибок во всех символах кодовых слов двухмодульных взвешенных кодов с суммированием, как при альтернативном варианте построения самопроверяемого устройства.

**Характеристики обнаружения ошибок в кодовых словах двухмодульными взвешенными кодами с суммированием.** Автоматизация процесса подсчета числа необнаруживаемых ошибок в символах кодовых слов позволила получить характеристические таблицы для двухмодульных кодов с суммированием с  $m = 6-15$ , по которым прослеживаются свойства обнаружения ошибок. В табл. 1 и 2 приведены данные для  $m = 8-10$ . Ошибки классифицированы по кратностям  $d$  и видам (по числу сочетаний искажений нулевых и единичных символов в кодовых словах) [19].

В табл. 1 приведены данные о числе необнаруживаемых ошибок с малыми кратностями  $N_d$ ,  $d = 2-5$ , а также об общем числе монотонных ( $N_v$ ), симметричных ( $N_\sigma$ ) и асимметричных ( $N_a$ ) ошибок в кодовых словах<sup>3</sup>;  $NCW$  и  $N^D$  — общее количество ошибок в кодовых словах и в информационных символах. На выходах реальных устройств возможны ошибки различных видов и с разными кратностями, что позволяет учитывать характеристики обнаружения кодами ошибок при синтезе самопроверяющего цифрового устройства. Отметим, что всего не обнаруживается  $2^m(2^m - 1)$  ошибок в кодовых словах для любых значений  $m$ , и для каждого двухмодульного взвешенного кода с одним и тем же  $m$ , но с разными значениями весовых коэффициентов взвешиваемого символа в первом и во втором подмножествах ( $w_1/w_2$ ), это число одинаково. Число необнаруживаемых ошибок, возникающих исключительно в информационных символах кодовых слов, значительно меньше, чем возникает во всех символах кодовых слов.

Таблица 1

| $m$ | $n$ | $w_1/w_2$ | $N_2$ | $N_3$ | $N_4$ | $N_5$  | $N_v$ | $N_\sigma$ | $N_a$  | $NCW$   | $N^D$ |

|-----|-----|-----------|-------|-------|-------|--------|-------|------------|--------|---------|-------|

| 8   | 12  | 1/1       | 2560  | 2560  | 7680  | 14080  | 5538  | 10006      | 49736  | 65280   | 4928  |

|     |     | 1/2       | 2304  | 2816  | 6528  | 13952  | 4878  | 10058      | 50344  | 65280   | 4352  |

|     |     | 1/3       | 2560  | 2560  | 7680  | 14080  | 5538  | 9994       | 49748  | 65280   | 4928  |

|     |     | 2/2       | 2048  | 3072  | 5632  | 13312  | 4290  | 10694      | 50296  | 65280   | 3840  |

|     |     | 2/3       | 2304  | 2816  | 6528  | 13952  | 4878  | 10398      | 50004  | 65280   | 4352  |

|     |     | 3/3       | 2560  | 2560  | 7680  | 14080  | 5538  | 10214      | 49528  | 65280   | 4928  |

| 9   | 13  | 1/1       | 6400  | 6400  | 24320 | 43520  | 13606 | 39828      | 208198 | 261632  | 19072 |

|     |     | 1/2       | 5632  | 7680  | 20480 | 44800  | 13606 | 40396      | 207630 | 261632  | 17920 |

|     |     | 1/3       | 6400  | 6400  | 24320 | 43520  | 17126 | 38176      | 206330 | 261632  | 19072 |

|     |     | 2/2       | 5120  | 8192  | 17664 | 42496  | 12010 | 41996      | 207626 | 261632  | 15872 |

|     |     | 2/3       | 5888  | 6912  | 20736 | 43264  | 15146 | 39492      | 206994 | 261632  | 17920 |

|     |     | 3/3       | 6400  | 6400  | 24320 | 43520  | 17126 | 38896      | 205610 | 261632  | 19072 |

| 10  | 14  | 1/1       | 15360 | 15360 | 72960 | 130560 | 33330 | 160332     | 853890 | 1047552 | 72960 |

|     |     | 1/2       | 13824 | 17920 | 61440 | 135680 | 33330 | 162948     | 851274 | 1047552 | 68608 |

|     |     | 1/3       | 15360 | 15360 | 72960 | 130560 | 41842 | 154032     | 851678 | 1047552 | 72960 |

|     |     | 2/2       | 12288 | 20480 | 52224 | 133120 | 33330 | 165868     | 848354 | 1047552 | 64512 |

|     |     | 2/3       | 13824 | 17920 | 61440 | 135680 | 41842 | 156408     | 849302 | 1047552 | 68608 |

|     |     | 3/3       | 15360 | 15360 | 72960 | 130560 | 52402 | 148644     | 846506 | 1047552 | 72960 |

В табл. 2 сведены некоторые относительные показатели обнаружения ошибок двухмодульными взвешенными кодами с суммированием. Параметр  $\beta_d$  характеризует долю необнаруживаемых ошибок с кратностью  $d = 2-5$  от общего числа ошибок с данной кратностью. Величины  $v$ ,  $\sigma$ ,  $\alpha$  представляют собой доли необнаруживаемых монотонных, симметричных и асимметричных ошибок от общего количества ошибок в кодовых словах;  $\eta$  и  $\gamma$  характеризуют

<sup>3</sup> Монотонная ошибка связана с искажениями только нулевых или только единичных символов в кодовых словах. Симметричная ошибка связана с искажениями одинакового количества нулевых и единичных символов в кодовых словах. Асимметричная ошибка связана с искажениями неравного количества нулевых и единичных символов в кодовых словах.

долях необнаруживаемых ошибок во всех символах кодовых слов и отдельно в информационных символах от общего количества ошибок, возникающих в кодовых словах.

Таблица 2

| $m$ | $n$ | $w_1/w_2$ | $\beta_2, \%$ | $\beta_3, \%$ | $\beta_4, \%$ | $\beta_5, \%$ | $v, \%$ | $\sigma, \%$ | $\alpha, \%$ | $\eta, \%$ | $\gamma, \%$ |

|-----|-----|-----------|---------------|---------------|---------------|---------------|---------|--------------|--------------|------------|--------------|

| 8   | 12  | 1/1       | 0,01526       | 0,01526       | 0,04579       | 0,08394       | 0,03302 | 0,05965      | 0,29652      | 0,3892     | 0,02938      |

|     |     | 1/2       | 0,01374       | 0,01679       | 0,03892       | 0,08318       | 0,02908 | 0,05996      | 0,30015      | 0,3892     | 0,02595      |

|     |     | 1/3       | 0,01526       | 0,01526       | 0,04579       | 0,08394       | 0,03302 | 0,05958      | 0,29659      | 0,3892     | 0,02938      |

|     |     | 2/2       | 0,01221       | 0,01832       | 0,03358       | 0,07937       | 0,02558 | 0,06376      | 0,29986      | 0,3892     | 0,02289      |

|     |     | 2/3       | 0,01374       | 0,01679       | 0,03892       | 0,08318       | 0,02908 | 0,06199      | 0,29812      | 0,3892     | 0,02595      |

|     |     | 3/3       | 0,01526       | 0,01526       | 0,04579       | 0,08394       | 0,03302 | 0,0609       | 0,29528      | 0,3892     | 0,02938      |

| 9   | 13  | 1/1       | 0,00954       | 0,00954       | 0,03624       | 0,06486       | 0,02028 | 0,05936      | 0,31028      | 0,3899     | 0,02842      |

|     |     | 1/2       | 0,00839       | 0,01145       | 0,03052       | 0,06677       | 0,02028 | 0,0602       | 0,30943      | 0,3899     | 0,02671      |

|     |     | 1/3       | 0,00954       | 0,00954       | 0,03624       | 0,06486       | 0,02552 | 0,05689      | 0,30749      | 0,3899     | 0,02842      |

|     |     | 2/2       | 0,00763       | 0,01221       | 0,02632       | 0,06333       | 0,0179  | 0,06259      | 0,30942      | 0,3899     | 0,02365      |

|     |     | 2/3       | 0,00877       | 0,0103        | 0,0309        | 0,06448       | 0,02257 | 0,05885      | 0,30848      | 0,3899     | 0,02671      |

|     |     | 3/3       | 0,00954       | 0,00954       | 0,03624       | 0,06486       | 0,02552 | 0,05797      | 0,30642      | 0,3899     | 0,02842      |

| 10  | 14  | 1/1       | 0,00572       | 0,00572       | 0,02718       | 0,04864       | 0,01242 | 0,05973      | 0,31812      | 0,3903     | 0,02718      |

|     |     | 1/2       | 0,00515       | 0,00668       | 0,02289       | 0,05055       | 0,01242 | 0,06071      | 0,31714      | 0,3903     | 0,02556      |

|     |     | 1/3       | 0,00572       | 0,00572       | 0,02718       | 0,04864       | 0,01559 | 0,05738      | 0,31729      | 0,3903     | 0,02718      |

|     |     | 2/2       | 0,00458       | 0,00763       | 0,01946       | 0,04959       | 0,01242 | 0,06179      | 0,31606      | 0,3903     | 0,02403      |

|     |     | 2/3       | 0,00515       | 0,00668       | 0,02289       | 0,05055       | 0,01559 | 0,05827      | 0,31641      | 0,3903     | 0,02556      |

|     |     | 3/3       | 0,00572       | 0,00572       | 0,02718       | 0,04864       | 0,01952 | 0,05538      | 0,31537      | 0,3903     | 0,02718      |

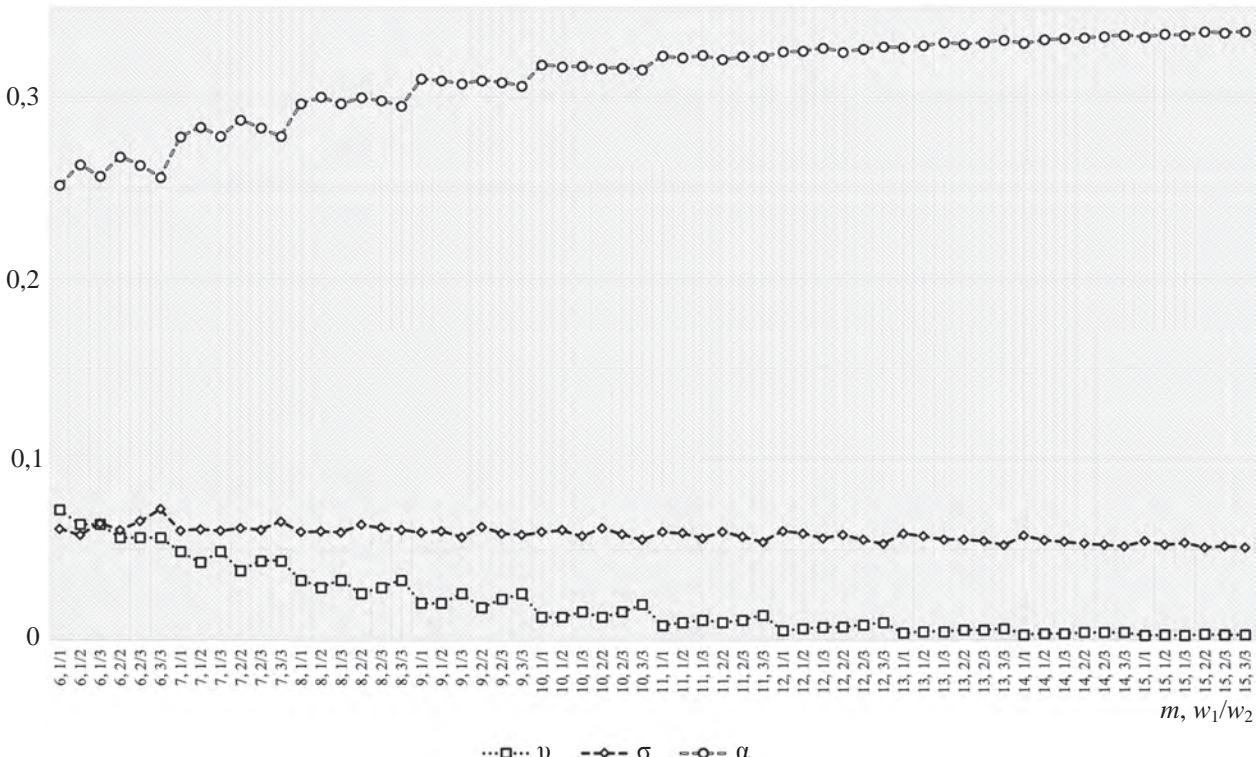

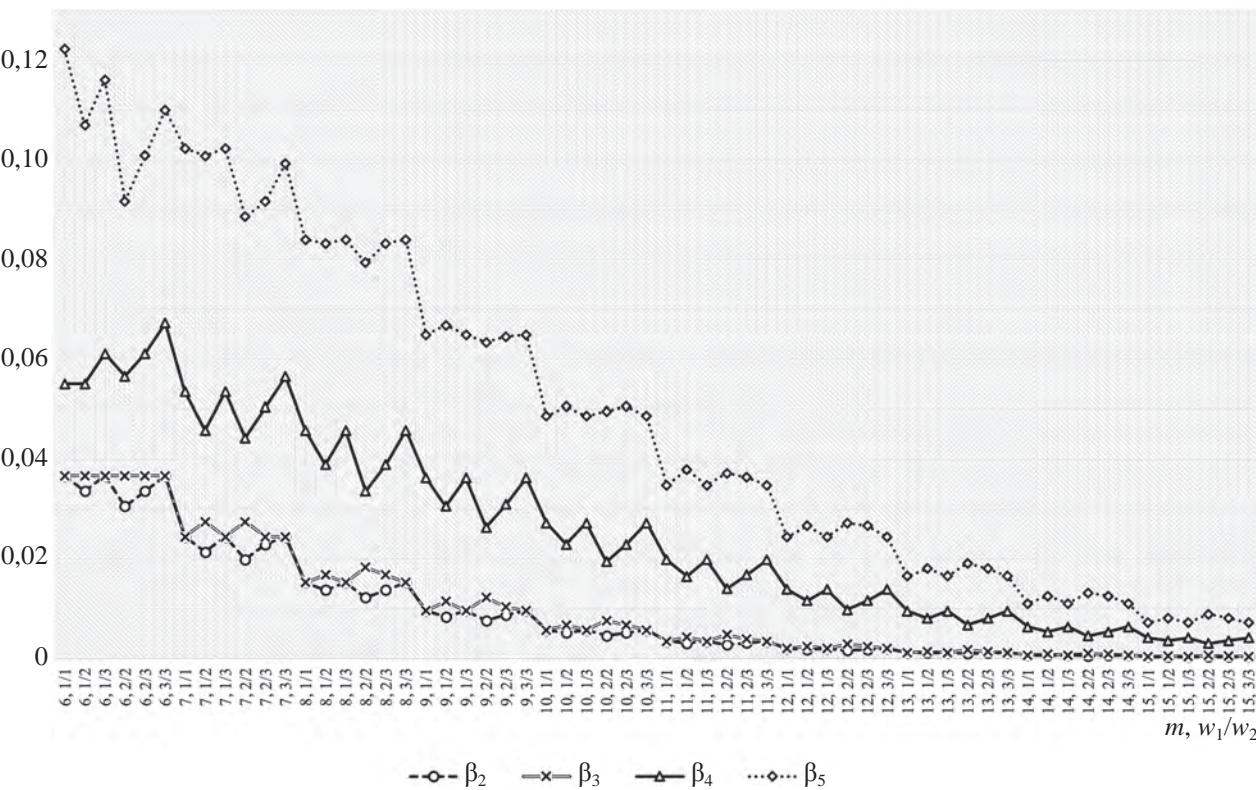

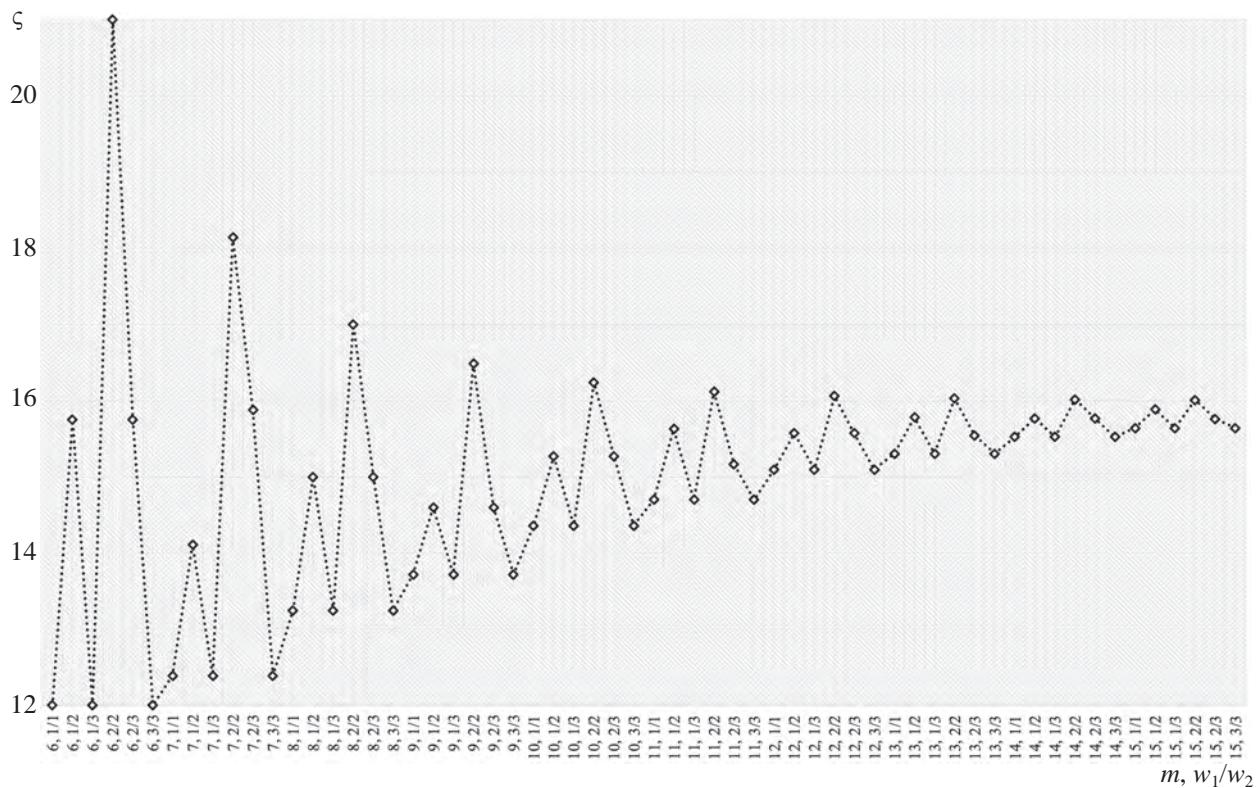

На рис. 3 и 4 приведены зависимости  $v$ ,  $\sigma$ ,  $\alpha$  и  $\beta_d$  ( $d = 2-5$ ) от  $m$  для двухмодульных кодов с суммированием при  $m = 6-15$ . График для коэффициента  $\zeta = \frac{N^{CW}}{N^D}$  (рис. 5) иллюстрирует, во сколько раз число необнаруживаемых ошибок, возникающих во всех символах кодовых слов, превышает число необнаруживаемых ошибок, возникающих исключительно в информационных символах.

Проанализировав рис. 3, можно сделать следующий вывод: величина  $\sigma$  с ростом  $m$  существенно не изменяется, находясь в пределах 0,05–0,06 %. Значения  $v$  и  $\alpha$  меняются уже гораздо заметнее: с ростом  $m$  величина  $v$  уменьшается, а  $\alpha$ , наоборот, возрастает. Другими словами, при  $m < 10$  монотонные ошибки имеют некоторую ощутимую долю среди общего числа необнаруживаемых ошибок в кодовых словах, а асимметричные доминируют среди всех остальных ( обратим внимание на то, что  $\alpha > 0,25\%$  для любых двухмодульных кодов, тогда как  $\sigma$  и  $v$  в разы меньше), но не настолько значительно, как при больших  $m$ .

Из рис. 4 видно, что показатель  $\beta_d$  при  $d = 2-5$  с ростом значения  $m$  снижается для всех  $d$ . Интересно, что  $\beta_2$  и  $\beta_3$  составляют самые малые доли необнаруживаемых ошибок среди всех остальных ошибок с другими кратностями. С учетом большей вероятности возникновения ошибок с малыми кратностями это характеризует двухмодульные коды с суммированием как высокоэффективные при организации СВК на основе ЛКС, так как эти коды будут „хорошо справляться“ с ошибками с малыми кратностями. В рис. 4 интересны „срезы“ для конкретных значений  $m$ . К примеру, для  $m = 10$  имеем:  $\beta_2 = 0,004\ 58-0,005\ 72$ ,  $\beta_3 = 0,005\ 72-0,007\ 63$ ,  $\beta_4 = 0,019\ 46-0,027\ 18$ ,  $\beta_5 = 0,048\ 64-0,050\ 55\%$ ; для  $m = 15$  имеем  $\beta_2 = 0,000\ 32-0,000\ 38$ ,  $\beta_3 = 0,000\ 38-0,000\ 58$ ,  $\beta_4 = 0,002\ 97-0,004\ 17$ ,  $\beta_5 = 0,007\ 18-0,008\ 85\%$ . Другими словами, с увеличением числа  $m$  на пять доля, например, двукратных ошибок от общего их количества уменьшилась на порядок.

$\nu, \sigma, \alpha, \%$

Рис. 3

$\beta_d, \%$

Рис. 4

С практической точки зрения не менее важен рис. 5: видно, что с ростом значения  $m$  наблюдается и постепенный рост диапазонов изменения величин  $\zeta = N^{CW}/N^D$  с разными сочетаниями  $w_1/w_2$ .

Более детальный учет характеристик двухмодульного кода с суммированием для выбранного значения  $m$  позволяет на практике выбирать наилучший способ построения СВК с учетом (1) и (2). Покажем, как можно использовать одно из свойств двухмодульного кода с суммированием — существенное превышение числа необнаруживаемых ошибок в символах кодовых слов по сравнению с числом необнаруживаемых ошибок в информационных символах.

**Метод выделения групп выходов для контроля вычислений на основе двухмодульных взвешенных кодов с суммированием.** Анализ зависимости  $\zeta$  (см. рис. 5) свидетельствует, что число необнаруживаемых двухмодульными кодами с суммированием ошибок в кодовых словах более чем в десять раз выше числа необнаруживаемых только в информационных символах ошибок. Поэтому при синтезе СВК на основе ЛКС целесообразно исключить одновременное возникновение ошибок в информационных и проверочных символах кодовых слов. В случае одиночной неисправности в любом компоненте объекта диагностирования это можно сделать, разделив физически выходы, которые участвуют в формировании информационных и проверочных символов кодовых слов. Тогда любая одиночная неисправность приведет к возникновению ошибки либо в группе непреобразуемых, либо в группе преобразуемых выходов. В первом случае ошибка будет обнаружена, так как приведет к нарушению соответствия между значениями информационных и проверочных символов: контрольный вектор не будет соответствовать информационному, так как ошибка всегда транслируется на выход элемента  $XOR$ . Во втором случае для обеспечения полной самопроверяемости необходимо исключить возникновение необнаруживаемых ошибок на выходах, которые не преобразуются.

Рис. 5

Для решения задачи обнаружения любых сочетаний искажений на выходах объекта диагностирования, формирующих информационные символы двухмодульных кодов, требуется

установить свойства распространения ошибок на непреобразуемые выходы объекта диагностирования, а также выполнить одно из следующих действий:

- 1) подобрать такой двухмодульный код, который будет обнаруживать все возможные виды ошибок на выходах;

- 2) выделить группы контролепригодных выходов по выбранному двухмодульному коду;

- 3) преобразовать структуру объекта диагностирования в структуру с контролепригодными группами выходов (вплоть до единственной группы, содержащей все выходы).

Из вышесказанного непосредственно следует, что характеристики обнаружения ошибок двухмодульными кодами исключительно в информационных символах, установленные в [9], будут определяющими при физическом разделении выходов, которые участвуют в формировании информационных и проверочных символов кодовых слов.

В [20] введены понятия структурно и функционально независимых групп выходов.

*Определение 1.* Группа выходов  $(f_{i_1}, f_{i_2}, \dots, f_{i_s})$ ,  $\{i_1, i_2, \dots, i_s\} \in \{1, 2, \dots, n\}$  структурно независима от группы выходов  $(f_{j_1}, f_{j_2}, \dots, f_{j_l})$ ,  $\{j_1, j_2, \dots, j_l\} \in \{1, 2, \dots, n\} \setminus \{i_1, i_2, \dots, i_s\}$ , если в структуре цифрового устройства не существует такого элемента, пути от которого ведут одновременно хотя бы к одному из выходов  $(f_{i_1}, f_{i_2}, \dots, f_{i_s})$  и хотя бы к одному из выходов группы  $(f_{j_1}, f_{j_2}, \dots, f_{j_l})$ .

Если имеется группа выходов  $(f_{i_1}, f_{i_2}, \dots, f_{i_s})$ , структурно не зависящая от группы выходов  $(f_{j_1}, f_{j_2}, \dots, f_{j_l})$ , то в качестве преобразуемых выходов могут быть выбраны выходы как первой, так и второй группы. Среди таких групп выполняется поиск тех выходов, которые следует преобразовывать с учетом влияния на сложность технической реализации блока  $G(X)$  и необходимости обеспечения контролепригодности тестера двухмодульного кода с суммированием и элементов  $XOR$ .

Среди структурно независимых выходов могут быть выделены функционально независимые выходы.

*Определение 2.* Группа выходов функционально независима, если все ее выходы либо структурно независимы от выходов, образующих другую группу, либо могут иметь пути, связывающие их и выходы из другой группы с одинаковыми логическими элементами структуры, но при этом ввиду особенностей реализуемых функций не допускающие возникновения одновременных искажений.

Сформулируем следующее важное положение.

*Теорема.* Группа выходов  $(f_a, f_b, \dots, f_k)$ ,  $a, b, \dots, k \in \{1, 2, \dots, n\}$  функционально независима от группы выходов  $(f_{i_1}, f_{i_2}, \dots, f_{i_v}) = \{f_1, f_2, \dots, f_n\} \setminus \{f_a, f_b, \dots, f_k\}$ , если  $\forall y_q, q \in Q$ :

$$\left( \frac{\partial f_a}{\partial y_q} \vee \frac{\partial f_b}{\partial y_q} \vee \dots \vee \frac{\partial f_k}{\partial y_q} \right) \left( \frac{\partial f_{i_1}}{\partial y_q} \vee \frac{\partial f_{i_2}}{\partial y_q} \vee \dots \vee \frac{\partial f_{i_v}}{\partial y_q} \right) = 0, \quad (3)$$

где  $y_q$  — функция, формируемая на выходах логического элемента  $G_q$  в структуре объекта диагностирования;  $Q$  — это множество индексов  $q$  элементов в структуре рассматриваемого устройства.

*Доказательство.* В левой части формулы (3) представлено произведение двух булевых выражений. В первом сомножителе присутствует дизъюнкция булевых производных для выделенной группы из  $k$  выходов. Во втором сомножителе приведена дизъюнкция булевых производных для оставшихся выходов. Ошибка, вызванная неисправностью элемента  $G_q$ , проявится на выходе  $f_i$  тогда и только тогда, когда  $\frac{\partial f_i}{\partial y_q} \neq 0$ . В этом случае булева производная будет равна некоторой булевой функции  $\frac{\partial f_i}{\partial y_q} \neq p_i$ . Искажения значений на выходе  $f_i$  будут возникать на тех входных комбинациях  $\langle X \rangle$ , на которых  $p_i(X) = 1$ . Если  $\frac{\partial f_a}{\partial y_q} \neq 0$  и  $\frac{\partial f_b}{\partial y_q} \neq 0$  то ошибка, вызванная неисправностью элемента  $G_q$ , проявится на выходах  $f_a$  и  $f_b$ . В этом случае  $\frac{\partial f_a}{\partial y_q} \vee \frac{\partial f_b}{\partial y_q} \neq 0$ . Данные

выходы будут зависимыми. Согласно определению 1, данная группа выходов будет независима от группы выходов  $(f_{i_1}, f_{i_2}, \dots, f_{i_v}) = \{f_1, f_2, \dots, f_n\} \setminus \{f_a, f_b\}$  если при возникновении неисправностей любых элементов искажаются только выходы  $f_a$  и  $f_b$ .

Продолжая цепочку умозаключений, получаем: если  $\frac{\partial f_a}{\partial y_q} \neq 0, \frac{\partial f_b}{\partial y_q} \neq 0, \dots, \frac{\partial f_k}{\partial y_q} \neq 0$ , то ошибка, вызванная неисправностью элемента  $G_q$ , проявится на выходах  $(f_a, f_b, \dots, f_k), a, b, \dots, k \in \{1, 2, \dots, n\}$ .

В этом случае  $\frac{\partial f_a}{\partial y_q} \vee \frac{\partial f_b}{\partial y_q} \vee \dots \vee \frac{\partial f_k}{\partial y_q} \neq 0$ .

Не должно существовать условий, при которых булевые производные по всем переменным для других выходов были бы не равны нулю:  $\frac{\partial f_i}{\partial y_q} = 0, i \in \{i_1, i_2, \dots, i_v\}$ . Тогда для всех выходов из группы справедливо выражение:  $\frac{\partial f_{i_1}}{\partial y_q} \vee \frac{\partial f_{i_2}}{\partial y_q} \vee \dots \vee \frac{\partial f_{i_v}}{\partial y_q} = 0$ . Отсюда становится ясным, что искаже-

ния будут возникать в одной из выделенных групп выходов,  $(f_a, f_b, \dots, f_k), a, b, \dots, k \in \{1, 2, \dots, n\}$  или  $(f_{i_1}, f_{i_2}, \dots, f_{i_v}) = \{f_1, f_2, \dots, f_n\} \setminus \{f_a, f_b\}$ , если  $\forall y_q, q \in Q$ , выполняется условие (3), что и требовалось доказать. ■

В рассматриваемом случае применения двухмодульных взвешенных кодов с суммированием  $k = 4$  требуется выделить четыре функционально независимых выхода.

Выделение групп структурно и функционально независимых выходов позволяет выполнить первое условие — исключение одновременных ошибок в информационном и проверочных символах двухмодульных кодов с суммированием. Выходы одной из независимых групп (например, включающей в себя малое число выходов устройства) относятся к преобразуемым, а выходы второй группы — к непреобразуемым в СВК.

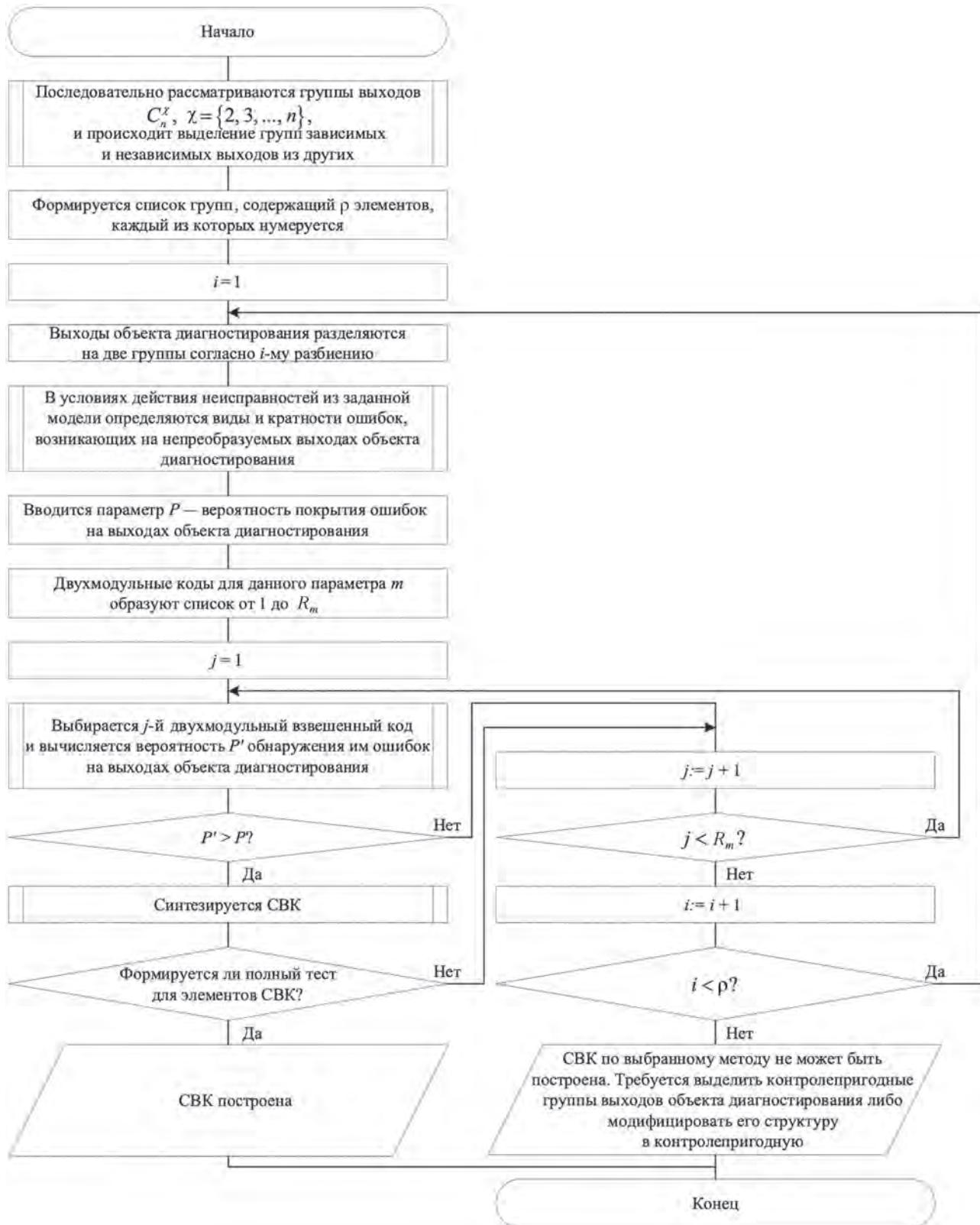

На рис. 6 приведена блок-схема алгоритма синтеза СВК на основе ЛКС с применением двухмодульных кодов с суммированием. Этот алгоритм позволяет синтезировать СВК с учетом тестируемости ее элементов. При этом может быть задано произвольное значение вероятности покрытия ошибок на выходах объекта диагностирования  $P$ , вплоть до  $P = 1$  (данному значению будет соответствовать полностью самопроверяемая структура СВК).

Остановка алгоритма условна, поскольку при достижении результата  $P' \geq P$  и наличии полного теста для элементов заканчивается построением СВК. Это упрощает его работу. Однако при отсутствии возможных вариантов синтеза СВК с заданным ограничением число операций существенно возрастает с увеличением числа выходов объекта диагностирования. Практическим ограничением работы алгоритма является число входов около 30–32 и число выходов объекта диагностирования около 22–25 — в зависимости от мощности вычислительной системы, на которой проектируется СВК (с развитием компьютерной техники и использованием, например, суперкомпьютеров или квантовых вычислителей данное ограничение оказывается несущественным). В случае превышения числа входов или выходов объекта диагностирования отмеченных параметров могут использоваться методы декомпозиции схемы устройства [21] с контролем вычислений на выходах отдельных подсхем.

**Экспериментальные результаты.** Важнейшей задачей, сопутствующей исследованиям особенностей двоичных избыточных кодов в СВК, является оценка структурной избыточности синтезируемых самопроверяемых устройств, а также контролепригодности элементов СВК. В ходе исследований авторы попытались решить ее, используя хорошо известную базу тестовых цифровых устройств MCNC Benchmarks [22]. При этом интерес представляло использование рассматриваемых в настоящей статье двухмодульных кодов с суммированием при синтезе СВК на основе ЛКС (в соответствии с альтернативным вариантом построения).

При оценке структурной избыточности самопроверяемых устройств применялись инструменты, имеющиеся в известном интерпретаторе SIS [23, 24]: оценка структурной избыточности производилась в условных единицах библиотеки stdcell2\_2.genlib, имеющих корреляцию с показателем площади, занимаемой устройством на кристалле.

Рис. 6

Для тестовых комбинационных схем были сгенерированы файлы-описания в формате \*.pla для всех блоков СВК, приведенной на рис. 2, а затем были определены показатели сложности их реализации. При синтезе СВК доопределение функций ЛКС оказывается однозначным, поскольку выделяемому информационному вектору соответствует единственный контрольный вектор. При получении файла-описания блока  $G(X)$  выходы контрольной схемы не переставлялись, при

этом последние  $k = 4$  выхода выделялись „под контрольный вектор“ (для преобразования), а оставшиеся  $m = n_{\text{out}} - 4$ , где  $n_{\text{out}}$  — число выходов контрольной схемы. Далее среди  $m$  выходов осуществлялось выделение  $\left\lceil \frac{m}{2} \right\rceil$  и  $\left\lfloor \frac{m}{2} \right\rfloor$  групп и взвешивание младших разрядов числами  $w_1/w_2$ .

Затем СВК строилась в соответствии с альтернативным вариантом на основе формируемого двухмодульного кода.

Экспериментально исследовано более двадцати тестовых комбинационных схем из MCNC Benchmarks. Были выбраны схемы с числом выходов  $n_{\text{out}} \geq 12$  и числом входов  $t \geq 6$ . При такой конфигурации целесообразно использовать двухмодульные коды с суммированием, а также возможно обеспечить тестируемость элементов преобразования в СВК (в табл. 3 приведены результаты экспериментов для трех из них).

Таблица 3

| Схема   | $w_1/w_2$ | $t$ | $n_{\text{out}}$ | $L_{F(X)}$ , усл. ед. | $L_{G(X)}$ , усл. ед. | $L_{CED}$ , усл. ед. | $L_D$ , усл. ед. | $\delta, \%$ |

|---------|-----------|-----|------------------|-----------------------|-----------------------|----------------------|------------------|--------------|

| m1      | 1/1       | 6   | 12               | 3064                  | 832                   | 5272                 | 8432             | 62,524       |

|         | 1/2       |     |                  |                       | 800                   | 5168                 |                  | 61,29        |

|         | 1/3       |     |                  |                       | 792                   | 5272                 |                  | 62,524       |

|         | 2/2       |     |                  |                       | 912                   | 5208                 |                  | 61,765       |

|         | 2/3       |     |                  |                       | 808                   | 5216                 |                  | 61,86        |

|         | 3/3       |     |                  |                       | 800                   | 5320                 |                  | 63,093       |

| max128  | 1/1       | 7   | 24               | 20192                 | 848                   | 23728                | 45184            | 52,514       |

|         | 1/2       |     |                  |                       | 1000                  | 23768                |                  | 52,603       |

|         | 1/3       |     |                  |                       | 888                   | 23808                |                  | 52,691       |

|         | 2/2       |     |                  |                       | 976                   | 23632                |                  | 52,302       |

|         | 2/3       |     |                  |                       | 888                   | 23696                |                  | 52,443       |

|         | 3/3       |     |                  |                       | 904                   | 23864                |                  | 52,815       |

| m4      | 1/1       | 8   | 16               | 18704                 | 4472                  | 24984                | 40544            | 61,622       |

|         | 1/2       |     |                  |                       | 4024                  | 24472                |                  | 60,359       |

|         | 1/3       |     |                  |                       | 4480                  | 25032                |                  | 61,74        |

|         | 2/2       |     |                  |                       | 4064                  | 24448                |                  | 60,3         |

|         | 2/3       |     |                  |                       | 4320                  | 24808                |                  | 61,188       |

|         | 3/3       |     |                  |                       | 4624                  | 25216                |                  | 62,194       |

| Среднее |           |     |                  |                       |                       |                      |                  | 58,657       |

Для каждой контрольной схемы был определен показатель сложности реализации  $L_{F(X)}$ . Отметим, что при этом не производилось какой-либо оптимизации структуры контрольной схемы. Далее вычислялись показатели сложности реализации кодера и блока  $G(X)$ . Так как показатель сложности реализации блока  $G(X)$  зависит от способа построения кода даже при одинаковых вариантах взвешивания символов, он оказывает существенное влияние на суммарные показатели структурной избыточности. Поэтому  $L_{G(X)}$  — показатель сложности реализации блока  $G(X)$  — приведен отдельно. На основании полученных данных с учетом обустройства СВК (см. рис. 2) определялся суммарный показатель сложности технической реализации самопроверяемого устройства  $L_{CED}$ .

Расчет осуществлялся аналогично тому, как это было сделано в работе [25]. Для сравнения приведены данные по показателю структурной избыточности самопроверяемого устройства  $L_D$ , синтезированного на основе классического метода дублирования. В последней графе табл. 3 приведены значения показателя  $\delta$ , характеризующего долю площади устройства, синтезиро-

ванного на основе ЛКС с применением двухмодульных взвешенных кодов с суммированием, от площади устройства, синтезированного на основе дублирования<sup>4</sup>.

Для всех контрольных схем самопроверяемое устройство, синтезированное на основе ЛКС с применением двухмодульных взвешенных кодов с суммированием, существенно проще устройства, синтезированного на основе дублирования. Изменение соотношения  $w_1/w_2$  позволяет несколько варьировать показатель сложности реализации, что выражается в изменении величины  $L_{G(X)}$ , а также показателя для кодера двухмодульного кода. В среднем для представленных в табл. 3 контрольных схем получено значение  $\delta = 58,657\%$ , свидетельствующее о весомом преимуществе использования ЛКС и двухмодульных кодов с суммированием перед дублированием по показателю структурной избыточности. Следует отметить, что для большинства тестовых схем получены именно такие результаты — попадание коэффициента  $\delta$  в диапазон 50–70 %.

Отдельно в ходе исследования анализировался показатель тестируемости элементов преобразования в СВК — элементов  $XOR$ . Следует отметить, что при изначальной неизменяемой конфигурации выходов устройства (без их перестановок) не всегда удавалось сформировать полный тест для всех элементов  $XOR$  при их канонической реализации [16].

В табл. 4 для примера приведены данные о числе входных комбинаций, на которых формировались те или иные тестовые комбинации для элементов  $XOR$ <sup>5</sup> одной из тестовых схем — „m1“. Возле значений весовых коэффициентов, для которых обеспечивается формирование полного множества тестовых комбинаций для всех элементов  $XOR$ , проставлен знак „\*“.

Таблица 4

| $w_1/w_2$ | Группа 1 |    |    |    | Группа 2 |         |    |    |    |    |

|-----------|----------|----|----|----|----------|---------|----|----|----|----|

|           | $XOR$    | 00 | 01 | 10 | 11       | $XOR$   | 00 | 01 | 10 | 11 |

| 1/1*      | $XOR_2$  | 47 | 2  | 1  | 14       | $XOR_8$ | 39 | 2  | 5  | 18 |

|           | $XOR_1$  | 39 | 6  | 3  | 16       | $XOR_7$ | 41 | 2  | 5  | 16 |

| 1/2       | $XOR_2$  | 47 | 2  | 1  | 14       | $XOR_8$ | 39 | 2  | 5  | 18 |

|           | $XOR_1$  | 39 | 6  | 3  | 16       | $XOR_7$ | 32 | 11 | 21 | 0  |

| 1/3       | $XOR_2$  | 47 | 2  | 1  | 14       | $XOR_8$ | 32 | 9  | 23 | 0  |

|           | $XOR_1$  | 39 | 6  | 3  | 16       | $XOR_7$ | 41 | 2  | 5  | 16 |

| 2/2       | $XOR_2$  | 44 | 5  | 4  | 11       | $XOR_8$ | 39 | 2  | 5  | 18 |

|           | $XOR_1$  | 41 | 4  | 2  | 17       | $XOR_7$ | 32 | 11 | 21 | 0  |

| 2/3       | $XOR_2$  | 44 | 5  | 4  | 11       | $XOR_8$ | 32 | 9  | 23 | 0  |

|           | $XOR_1$  | 41 | 4  | 2  | 17       | $XOR_7$ | 41 | 2  | 5  | 16 |

| 3/3       | $XOR_2$  | 45 | 4  | 4  | 11       | $XOR_8$ | 32 | 9  | 23 | 0  |

|           | $XOR_1$  | 39 | 6  | 3  | 16       | $XOR_7$ | 41 | 2  | 5  | 16 |

Для большинства рассмотренных схем обеспечить полную тестируемость элементов преобразования не удалось, однако следует отметить возможности перестановки выходов, которые в эксперименте не производились. С учетом высокого „запаса эффективности“ по структурной избыточности при использовании ЛКС и двухмодульных взвешенных кодов с суммированием, по сравнению с дублированием при перестановке выходов и выборе различных способов взвешивания разрядов информационного вектора, можно обеспечить полную самопроверяемость СВК.

<sup>4</sup> При расчетах были использованы несколько модифицированная формула (1), а также формулы (2) и (3) из [25].

<sup>5</sup> Индекс элемента  $XOR$  соответствует номеру преобразуемого выхода контрольной схемы.

Необходимо отметить, что наиболее сложным является обеспечение полной самопроверяемости СВК, синтезированной на основе ЛКС с применением двухмодульных взвешенных кодов. Например, задача формирования полного теста для тестера двухмодульного взвешенного кода с суммированием решается для каждой конкретной его структуры, а для некоторых способов синтеза может и вовсе оказаться нерешаемой. Это требует реализации тестера двухмодульного взвешенного кода с суммированием в виде высоконадежной структуры, где будут использованы методы внутреннего резервирования, элементы с более низкими значениями интенсивности потоков отказов и другие способы обеспечения высокой надежности функционирования.

**Заключение.** Применение двухмодульных кодов с суммированием при синтезе СВК может оказаться весьма эффективным. При этом целесообразно учитывать характеристики обнаружения двухмодульными кодами с суммированием как во всех символах кодовых слов, так и исключительно в информационных символах. Поскольку число не обнаруживаемых этими кодами ошибок, возникающих в информационных символах при безошибочности проверочных символов, значительно ниже числа необнаруживаемых ошибок, связанных с искажениями, и информационных, и проверочных символов, целесообразно при использовании варианта на основе ЛКС выделять группы функционально независимых выходов. В этом случае эффективным окажется учет ошибок, возникающих исключительно в информационных символах, а все остальные ошибки будут обнаружены в СВК. Несмотря на обозначенные особенности, в силу того что двухмодульные взвешенные коды с суммированием не обнаруживают менее 0,4 % ошибок в кодовых словах (если рассматривать весь диапазон значений  $m = 6-15$ , а не только данные табл. 2), также можно учитывать данные коды при синтезе СВК без выделения каких бы то ни было групп.

Дальнейшие исследования могут быть связаны с анализом характеристик двухмодульных кодов с иными разбиениями информационных символов на подмножество, а также полученных при использовании других модулей счета.

Полученные авторами результаты расширяют теорию синтеза самопроверяемых цифровых устройств и дают их разработчику еще одну „группу“ методов синтеза. При этом, как отмечалось выше, создаются условия построения полностью самопроверяемых структур даже в тех случаях, когда этого не удается добиться известными методами [4].

## СПИСОК ЛИТЕРАТУРЫ

1. *Piestrak S. J. Design of Self-Testing Checkers for Unidirectional Error Detecting Codes.* Wrocław: Oficyna Wydawnicza Politechniki Wrocławskiej, 1995. 111 p.

2. *Fujiwara E. Code Design for Dependable Systems: Theory and Practical Applications.* John Wiley & Sons, 2006. 720 p.

3. *Göessel M., Ocheretny V., Sogomonyan E., Marienfeld D. New Methods of Concurrent Checking:* Edition 1. Dordrecht: Springer Science+Business Media B.V., 2008. 184 p.

4. *Согомонян Е. С., Слабаков Е. В. Самопроверяемые устройства и отказоустойчивые системы.* М.: Радио и связь, 1989. 208 с.

5. *Сапожников В. В., Сапожников Вл. В., Ефанов Д. В. Коды с суммированием для систем технического диагностирования. Т. 1: Классические коды Бергера и их модификации.* М.: Наука, 2020. 383 с.

6. *Сапожников В. В., Сапожников Вл. В., Ефанов Д. В. Коды с суммированием для систем технического диагностирования. Т. 2: Взвешенные коды с суммированием.* М.: Наука, 2021. 455 с.

7. *Efanov D., Sapozhnikov V., Sapozhnikov Vl. Generic Two-Modulus Sum Codes for Technical Diagnostics of Discrete Systems Problems // Proceedings of 14th IEEE East-West Design & Test Symposium (EWCTS'2016).* Yerevan, Armenia, 14–17 October, 2016. P. 256–260. DOI: 10.1109/EWCTS.2016.7807713.

8. *Efanov D. V., Sapozhnikov V. V., Sapozhnikov Vl. V. Two-Modulus Codes with Summation of One-Data Bits for Technical Diagnostics of Discrete Systems // Automatic Control and Computer Sciences.* 2018. Vol. 52, is. 1. P. 1–12. DOI: 10.3103/S0146411618010029.

9. *Ефанов Д. В., Сапожников В. В., Сапожников Вл. В. Двухмодульные взвешенные коды с суммированием в кольце вычетов по модулю  $M=4$  // Труды СПИИРАН.* 2020. Т. 19, № 3. С. 674–713. DOI: 10.15622/sp.2020.19.3.8.

10. *Ефанов Д. В., Тимошенков М. В., Сиваченко Л. А., Лесковец И. В. Исследование двухмодульных взвешенных кодов с суммированием с произвольными разбиениями множества информационных символов // Автоматика на транспорте.* 2023. Т. 9, № 4. С. 377–389. DOI: 10.20295/2412-9186-2023-9-04-377-389.

11. Berger J. M. A Note on Error Detection Codes for Asymmetric Channels // Information and Control. 1961. Vol. 4, is. 1. P. 68–73. DOI: 10.1016/S0019-9958(61)80037-5.

12. Блюдов А. А., Ефанов Д. В., Сапожников В. В., Сапожников Вл. В. О кодах с суммированием единичных разрядов в системах функционального контроля // Автоматика и телемеханика. 2014. № 8. С. 131–145.

13. Гессель М., Морозов А. В., Сапожников В. В., Сапожников Вл. В. Логическое дополнение – новый метод контроля комбинационных схем // Автоматика и телемеханика. 2003. № 1. С. 167–176.

14. Гессель М., Морозов А. В., Сапожников В. В., Сапожников Вл. В. Контроль комбинационных схем методом логического дополнения // Автоматика и телемеханика. 2005. № 8. С. 161–172.

15. Mitra S., McCluskey E.J. Which Concurrent Error Detection Scheme to Choose? // Proceedings of International Test Conference. USA, Atlantic City, NJ, 03–05 October 2000. P. 985–994. DOI: 10.1109/TEST.2000.894311.

16. Аксёнова Г. П. Необходимые и достаточные условия построения полностью проверяемых схем свертки по модулю 2 // Автоматика и телемеханика. 1979. № 9. С. 126–135.

17. Dhar K. Design of a low Power, High Speed and Energy Efficient 3 Transistor XOR Gate in 45nm Technology Using the Conception of MVT Methodology // 2014 International Conference on Control, Instrumentation, Communication and Computational Technologies (ICCICCT). Kanyakumari, India, 10–11 July 2014. DOI: 10.1109/ICCICCT.2014.6992931.

18. Ефанов Д. В., Сапожников В. В., Сапожников Вл. В. Применение модульных кодов с суммированием для построения систем функционального контроля комбинационных логических схем // Автоматика и телемеханика. 2015. № 10. С. 152–169.

19. Сапожников В. В., Сапожников Вл. В., Ефанов Д. В. Классификация ошибок в информационных векторах систематических кодов // Изв. вузов. Приборостроение. 2015. Т. 58, № 5. С. 333–343. DOI: 10.17586/0021-3454-2015-58-5-333-343.

20. Efanov D. V., Sapozhnikov V. V., Sapozhnikov Vl. V. The Self-Checking Concurrent Error-Detection Systems Synthesis Based on the Boolean Complement to the Bose-Lin Codes with the Modulo Value M=4 // Electronic Modeling. 2021. Vol. 43, is. 1. P. 28–45. DOI: 10.15407/emodel.43.01.028.

21. Закревский А. Д., Потосин Ю. В., Черемисинова Л. Д. Логические основы проектирования дискретных устройств. М.: Физматлит, 2007. 592 с.

22. Collection of Digital Design Benchmarks [Электронный ресурс]: <<https://ddd.fit.cvut.cz/www/prj/Benchmarks/>>.

23. Sentovich E. M., Singh K. J., Moon C., Savoj H., Brayton R. K., Sangiovanni-Vincentelli A. Sequential Circuit Design Using Synthesis and Optimization // Proceedings IEEE International Conference on Computer Design: VLSI in Computers & Processors. Cambridge, MA, USA, 11–14 October 1992. P. 328–333. DOI: 10.1109/ICCD.1992.276282.

24. Sentovich E. M., Singh K. J., Lavagno L., Moon C., Murgai R., Saldanha A., Savoj H., Stephan P. R., Brayton R. K., Sangiovanni-Vincentelli A. SIS: A System for Sequential Circuit Synthesis. Electronics Research Laboratory, Department of Electrical Engineering and Computer Science, University of California, Berkeley, 4 May 1992. 45 p.

25. Ефанов Д. В., Елина Е. И. Исследование алгоритмов синтеза самопроверяемых цифровых устройств на основе логической коррекции сигналов с применением взвешенных кодов Боуза–Лина // Автоматика на транспорте. 2024. Т. 10, № 1. С. 74–99. DOI: 10.20296/2412-9186-2024-10-01-74-99.

## СВЕДЕНИЯ ОБ АВТОРАХ

**Дмитрий Викторович Ефанов**

— д-р техн. наук, профессор; Российский университет транспорта, кафедра „Автоматика, телемеханика и связь на железнодорожном транспорте“; профессор; Санкт-Петербургский политехнический университет Петра Великого, Высшая школа транспорта Института машиностроения, материалов и транспорта; профессор; E-mail: TrES-4b@yandex.ru

**Марина Владимировна Зуева**

— Банк „Санкт-Петербург“; программист-аналитик; E-mail: marina-seo-media@yandex.ru

**Есения Игоревна Елина**

— аспирант; Санкт-Петербургский политехнический университет Петра Великого, Высшая школа транспорта Института машиностроения, материалов и транспорта; E-mail: eseniya-elina@mail.ru

**Максим Викторович Тимошенков**

— магистрант; Санкт-Петербургский политехнический университет Петра Великого, Высшая школа транспорта Института машиностроения, материалов и транспорта; E-mail: timych180@gmail.com

Поступила в редакцию 13.05.24; одобрена после рецензирования 12.07.24; принята к публикации 27.02.25.

## REFERENCES

1. Piestrak S.J. *Design of Self-Testing Checkers for Unidirectional Error Detecting Codes*, Wrocław, Oficyna Wydawnicza Politechniki Wrocławskiej, 1995, 111 p.

2. Fujiwara E. *Code Design for Dependable Systems: Theory and Practical Applications*, John Wiley & Sons, 2006, 720 p.

3. Göessel M., Ocheretny V., Sogomonyan E., Marienfeld D. *New Methods of Concurrent Checking*. Edition 1, Dordrecht: Springer Science+Business Media B.V., 2008, 184 p.

4. Sogomonyan E.S., Slabakov E.V. *Samoprovaryaemye ustroystva i otkazoustoychivye sistemy* (The Self-Checked Devices and Failure-Safe Systems), Moscow, 1989, 208 p. (in Russ.)

5. Sapozhnikov V.V., Sapozhnikov VI.V., Efandov D.V. *Kody s summirovaniyem dlya sistem tekhnicheskogo diagnostirovaniya. T. 1. Klassicheskiye kody Bergera i ikh modifikatsii* (Summed Codes for Technical Diagnostic Systems. Vol. 1. Classical Berger Codes and Their Modifications), Moscow, 2020, 383 p. (in Russ.)

6. Sapozhnikov V.V., Sapozhnikov VI.V., Efandov D.V. *Kody s summirovaniyem dlya sistem tekhnicheskogo diagnostirovaniya. T. 2. Vzveshennyye kody s summirovaniyem* (Summed Codes for Technical Diagnostic Systems. Vol. 2. Weighted Codes with Summation), Moscow, 2021, 455 p. (in Russ.)

7. Efandov D., Sapozhnikov V., Sapozhnikov VI. *Proceedings of 14th IEEE East-West Design & Test Symposium (EWDTs'2016)*, Yerevan, Armenia, October 14–17, 2016, pp. 256–260, doi: 10.1109/EWDTs.2016.7807713.

8. Efandov D.V., Sapozhnikov V.V., Sapozhnikov VI.V. *Automatic Control and Computer Sciences*, 2018, no. 1(52), pp. 1–12, DOI: 10.3103/S0146411618010029.

9. Efandov D.V., Sapozhnikov V.V., Sapozhnikov VI.V. *Trudy SPIIRAN (SPIIRAS Proceedings)*, 2020, no. 3(19), pp. 674–713, DOI: 10.15622/sp.2020.19.3.8. (in Russ.)

10. Efandov D.V., Timoshenkov M.V., Sivachenko L.A., Leskovets I.V. *Automation on transport*, 2023, no. 4(9), pp. 377–389, DOI: 10.20295/2412-9186-2023-9-04-377-389. (in Russ.)

11. Berger J.M. *Information and Control*, 1961, no. 1(4), pp. 68–73, DOI: 10.1016/S0019-9958(61)80037-5.

12. Blyudov A.A., Efandov D.V., Sapozhnikov V.V. *Automation and Remote Control*, 2014, no. 8(75), pp. 1460–1470.

13. Gessel M., Morozov A.V., Sapozhnikov V.V. & Sapozhnikov VI.V. *Automation and Remote Control*, 2003, no. 1(64), pp. 153–161, DOI: <https://doi.org/10.1023/A:102184727370>.

14. Goessel M., Morozov A.V., Sapozhnikov V.V. & Sapozhnikov VI.V. *Automation and Remote Control*, 2005, no. 8(66), pp. 1336–1346, DOI: <https://doi.org/10.1007/s10513-005-0174-2>.

15. Mitra S., McCluskey E.J. *Proceedings of International Test Conference*, 2000, USA, Atlantic City, NJ, 03–05 October 2000, pp. 985–994, DOI: 10.1109/TEST.2000.894311.

16. Aksyonova G.P. *Automation and Remote Control*, 1979, no. 9, pp. 126–135. (in Russ.)

17. Dhar K. *2014 International Conference on Control, Instrumentation, Communication and Computational Technologies (ICCI CCT)*, 10–11 July 2014, Kanyakumari, India, DOI: 10.1109/ICCI CCT.2014.6992931.

18. Efandov D.V., Sapozhnikov V.V. *Automation and Remote Control*, 2015, no. 10, pp. 1834–1848.

19. Sapozhnikov V.V., Sapozhnikov VI.V., Efandov D.V. *Journal of Instrument Engineering*, 2015, no. 5(58), pp. 333–343, DOI: 10.17586/0021-3454-2015-58-5-333-343. (in Russ.)

20. Efandov D.V., Sapozhnikov V.V., Sapozhnikov VI.V. *Electronic Modeling*, 2021, no. 1(43), pp. 28–45, DOI: 10.15407/ emodel.43.01.028.

21. Zakrevsky A.D., Pottosin Yu.V., Cheremisinova L.D. *Logicheskiye osnovy proyektirovaniya diskretnykh ustroystv* (Logical Foundations of Discrete Device Design), Moscow, 2007, 592 p. (in Russ.)

22. Collection of Digital Design Benchmarks, <https://ddd.fit.cvut.cz/www/prj/Benchmarks/>.

23. Sentovich E.M., Singh K.J., Moon C., Savoj H., Brayton R.K., Sangiovanni-Vincentelli A. *Proceedings IEEE International Conference on Computer Design: VLSI in Computers & Processors*, 11–14 October 1992, Cambridge, MA, USA, pp. 328–333, DOI: 10.1109/ICCD.1992.276282.

24. Sentovich E.M., Singh K.J., Lavagno L., Moon C., Murgai R., Saldanha A., Savoj H., Stephan P.R., Brayton R.K., Sangiovanni-Vincentelli A. *SIS: A System for Sequential Circuit Synthesis*, Electronics Research Laboratory, Department of Electrical Engineering and Computer Science, University of California, Berkeley, 4 May 1992, 45 p.

25. Efandov D.V., Elina E.I. *Transport automation research*, 2024, no. 1(10), pp. 74–99, DOI: 10.20296/2412-9186-2024-10-01-74-99. (in Russ.)

## DATA ON AUTHORS

**Dmitry V. Efandov**

— Dr. Sci., Professor; Russian University of Transport, Department of Automation, Remote Control, and Communications on Railway Transport; Professor; Peter the Great St. Petersburg Polytechnic University, Institute of Machinery, Materials, and Transport, Higher School of Transport; Professor; E-mail: TrES-4b@yandex.ru

**Marina V. Zueva**

— Bank Saint Petersburg PJSC; Programmer-Analyst; E-mail: marina-seo-media@yandex.ru

**Yeseniya I. Yelina**

— Post-Graduate Student; Peter the Great St. Petersburg Polytechnic University, Institute of Machinery, Materials, and Transport, Higher School of Transport; E-mail: eseniya-elina@mail.ru

**Maxim V. Timoshenkov**

— Master's Student; Peter the Great St. Petersburg Polytechnic University, Institute of Machinery, Materials, and Transport, Higher School of Transport; E-mail: timych180@gmail.com

Received 13.05.24; approved after reviewing 12.07.24; accepted for publication 27.02.25.